조합논리회로 (Combinational Circuits)

- 입력에 의해 출력이 결정

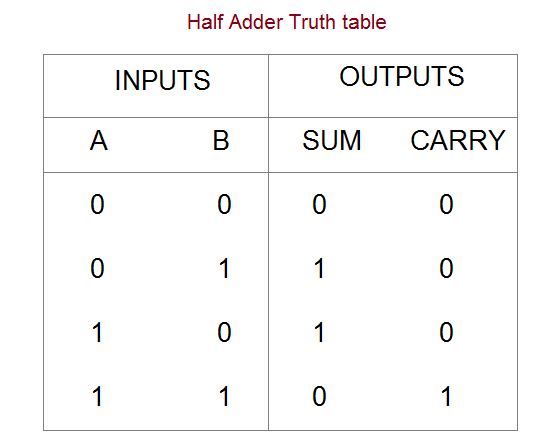

Half Adder

- 2개의 비트를 산술연산

S = x xor y = x’y + xy’

C = xy - 진리표

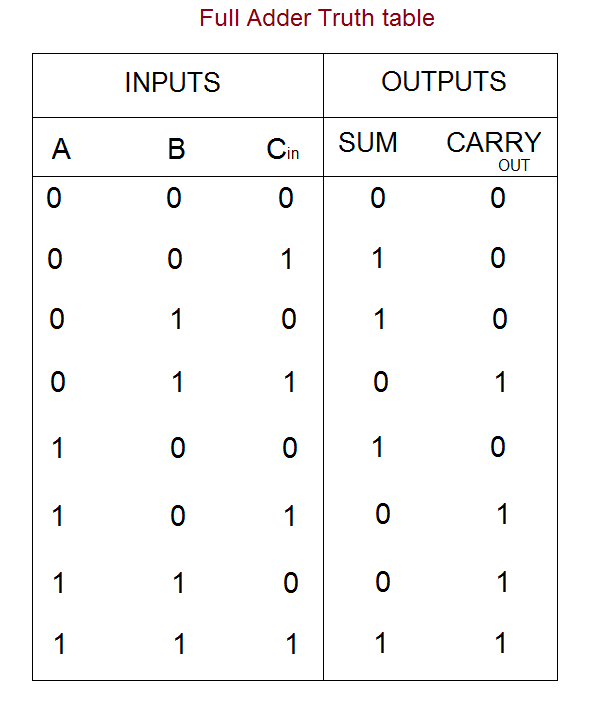

Full Adder

3개의 비트를 산술연산

S = x xor y xor z = x’y’z + x’yz’ + xy’z’ + xyz

C = xy + xz + yz진리표

순서논리회로 (Sequential Circuits)

- 피드백(Feedback)을 가진 조합회로로 구성

- 입력 값과 현재 기억 상태에 따라 출력이 결정

Flip-Flop

- 1비트를 기억하는 소자

- clock pulse generator에 의해 synchronization이 일어남

- 래치라고도 함

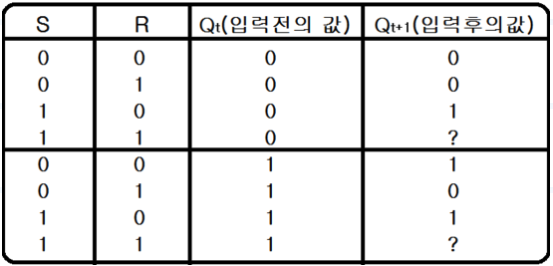

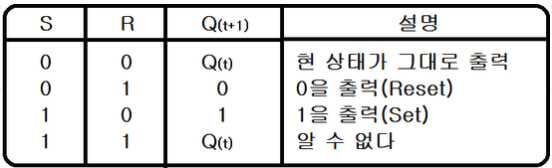

SR Flip-Flop

- R(Reset)과 S(Set) 두 입력을 받아서 Q(현재 상태)와 Q’(다음 상태)의 2가지 출력을 가진다

- 진리표

- 특성표

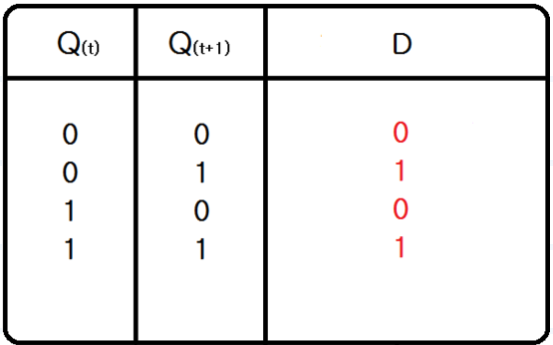

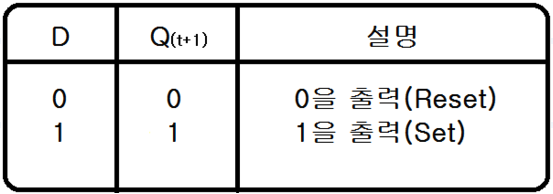

D Flip-Flop

- 특성표

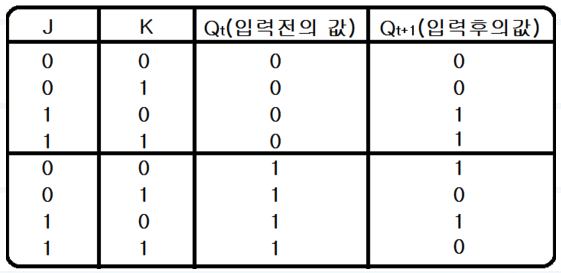

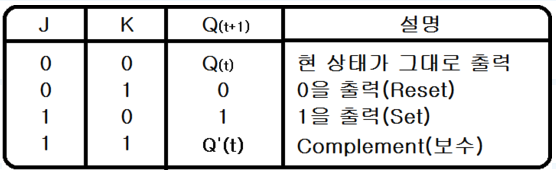

JK Flip-Flop

- RS 플립플롭보다 많이 쓰이는 플립플롭(RS플립플롭의 문제점 보완)

- 진리표

- 특성표

Level-triggering vs Edge-triggering

- 클락이 올라갈 때 positie

- 클락이 내려갈 때 negative

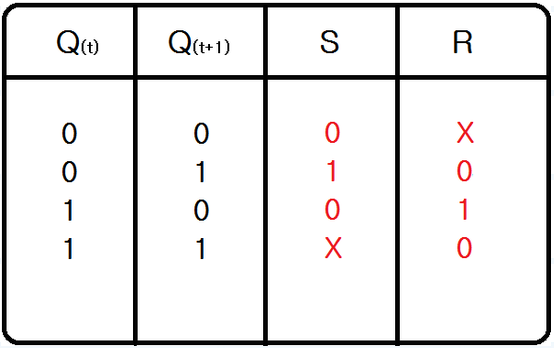

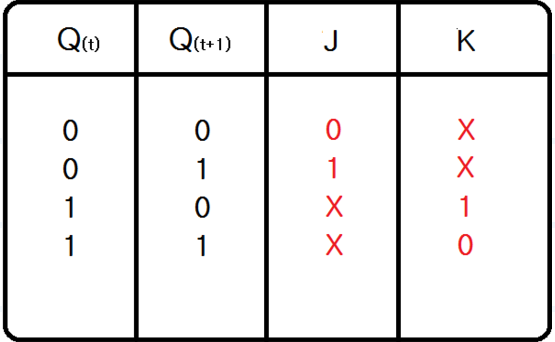

Excitation table

- 플립플롭에서 현 상태와 다음 상태를 알 때 플립플롭에 어떤 입력을 넣어야 하는가를 나타냄

- RS 플립플롭의 excitation table

- JK 플립플롭의 excitation table

- D 플립플롭의 excitation table