Modern Computer Systems

- Consists of CPUs, Main Memory, other devices

- Connected by a bus to access Main Memory

- CPU and devices(controllers) execute simultaneosly and compete for shared memory

- Memory controller unit(MMU) ensures these orders

Basic Understanding

- OS(image) is stored in HDD(SSD)

- When power is off, MM is empty(volatile) => so, when power is on, CPU can do nothing

- Thus, to start computer, OS image must be loaded into MM

Bootstrap program

- 하드웨어 제조사에서 개발

- First program to run when power is on

- Stored in Boot-ROM

- Initializes computer system hardware (OS가 초기화 하지 않는 이유? 하드웨어는 제조사별로 다양하기 때문에 OS가 일괄적으로 초기화 불가능)

- Loads OS from HDD(SSD) to first location of MM (addr = 0 or predefined)

What does CPU do?

- Fetch Instr.=> Decode => Fetch Data => Execute => Store

Fetch Instrunction

AR <- PC & IR <- M[AR] & PC++

OS Booting

- CPU simply fetch, decode, execute, store each line of OS image

- Activates scheduler(=swapper)(pid=0), first process init()(pid=1)

- Waits for interrupts to occur

- Hardware interrupts: signals CPU by bus

- Software interrupts: signals by sys calls(traps)

- Modern OSs are interrupt-driven

- Why interrupts necessary? : OS가 효율적으로 작동하기 위해

- When interrupts necessary? : CPU가 요청한 operation을 I/O controller가 다 끝냈을 때

Memory Mapped I/O

Case1: CPU가 Memory Mapped I/O를 직접 수행

키보드를 예시로 들면,

키보드 컨트롤 레지스터로 보내기 위해 AC에 1을 저장

AC로부터 키보드 컨트롤 레지스터에게 1을 보냄 (CPU가 키보드에게 유저로부터 character를 받기 시작한다고 말해주는 것)

CPU가 키보드 컨트롤 레지스터로부터 내용을 읽어들임

MSB=1이면, 유저가 입력한 character가 데이터 레지스터로 입력되고 데이터 레지스터로부터 데이터를 읽어들임

MSB=0이면, 유저로부터 입력받은 character가 없음

Device contorllers

- CPU로부터 명령을 받아 IO를 수행하고 상태를 유지

- IO logic, Buffer(data register), status register로 구성

- device controller의 operation이 끝나면 status register를 1로 세팅해 IO의 완료를 알림(interrupt)

I/O의 종류

Synchronous I/O

- Control is returned to user process only at completion of I/O

- 한 번에 한 개의 인터럽트밖에 수행하지 못 함

Asynchronous I/O

- 현대 OS에 쓰임

- Control is returned to another user process without waiting completion of I/O that it requested.

- Multiple I/O may exist by multiple process(multiple interrupts may take place)

Interrupt servicing procedure

인터럽트 signal이 CPU에 도착

OS가 리턴 어드레스를 저장 (push(stk_ptr, PC))

CPU가 도착한 인터럽트 타입을 조사

3-1) Polling

- 모든 device는 서로 같은 signal을 보냄

- CPU가 모든 device를 조사

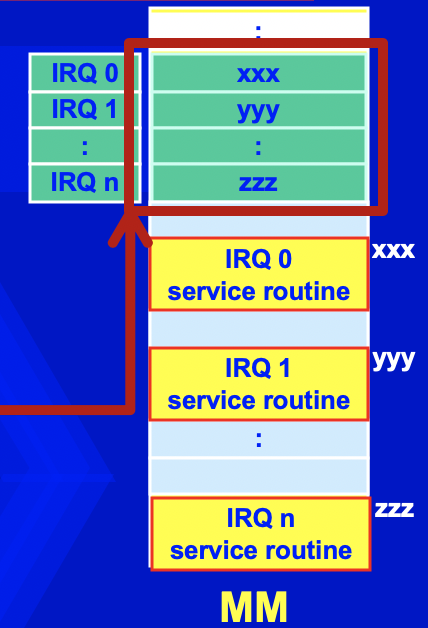

3-2) Vectored Interrupt

모든 인터럽트는 unique id가 부여(IRQ n)

device마다 서로 다른 signal을 보냄

signal이 도착하면 CPU는 인터럽트 벡터를 확인해 interrupt service routine(ISR)의 시작 주소를 얻음.

ISR 실행 (PC = some_address)

인터럽트 서비스가 끝나면 CPU는 다시 바로 전의 프로세스로 돌아감 (PC = pop(stk_ptr))

Multiple IO Management

- OS는 DST(Device-Status Table)라는 것을 유지

- 이 테이블 안에는 여러 device의 상태정보를 저장

- DST pointer 사용

DMA structure

CPU는 MM<-> Buffer in device controller간 데이터를 이동시키기엔 너무 아까움

MM은 CPU가 주로 쓴다

MM은 1 word씩 전송하므로 다른 장치들이 MM을 사용할 경우, CPU의 동작에 큰 영향

DMA controller는 CPU를 쓰지 않고 직접 MM과 Buffer에 접근해 데이터를 전송

CPU가 메모리를 쓰지 않을때 Cycle Stealing해 메모리에 접근하고 접근이 완료됐을 때 interrupt를 일으켜 작업완료를 알림

Disk Read operation summary

1-유저 CPU가 유저 프로세스 a를 실행하는 도중 IO instruction을 보면 IO가 일어남

컨텍스트 스위치가 일어남

2-커널 CPU가 device controller에 있는 레지스터를 로드하기 위해 OS 프로세스 A를 실행시킴

3-커널 CPU가 DST(device-status table)을 조정하기 위해 OS 프로세스 B를 실행시킴

컨텍스트 스위치가 일어남

4-유저 CPU가 새로운 유저 프로세스 b를 실행시켰다고 하면

5-디바이스 device controller가 레지스터를 decode하고 어떤 명령이 필요한지 인식

6-디바이스 device controller가 512 바이트를 디스크에서 local buffer로 이동

7-디바이스 device controller가 CPU에게 인터럽트 시그널을 보냄

8-유저 CPU는 유저 프로세스 b가 인터럽트된 것을 인식

컨텍스트 스위치가 일어남

9-커널 CPU가 어떤 인터럽트인지 조사하기 위해 OS 프로세스 C를 실행시킴

10-커널 CPU가 ISR(interrupt service routine)를 실행하기 위해 OS 프로세스 D를 실행시킴

ISR이 끝나면 DMA가 실행됌

컨텍스트 스위치가 일어남

11-유저 CPU는 8번에서 인터럽트된 유저 프로세스 b를 다시 실행시킴

DMA는 CPU와 무관하게 실행되고 있다가 512 바이트가 controller buffer에서 MM으로 옮겨지면 CPU에게 인터럽트 시그널을 보냄

12-유저 CPU는 유저 프로세스 b가 인터럽트된 것을 인식

컨텍스트 스위치가 일어남

13-커널 CPU가 DST를 조사하기위해 OS 프로세스 E를 실행시킴

14-커널 CPU는 8번에서 인터럽트된 유저 프로세스 b를 다시 실행하기 위해 OS 프로세스 F를 실행함

컨텍스트 스위치가 일어남

15-유저 CPU가 유저 프로세스 b를 다시 실행시킴